What's new

Year 2021 |

Certified as Research Institute (2021.04)

-

We are certified as a Research Institute from the Korea Industrial Technology Association (KOITA).

Certified as Venture Business (2021.04)

-

We are certified as a Vencture Business from the Ministry of MSEs and Startups of Korea.

-

Patent granted (March 2021)

-

A patent of "FRAME SYNCHRONIZATION SIGNAL INSERSION DEVICE AND METHOD OF TOMOGRAPHY SYSTEM" is granted.

-

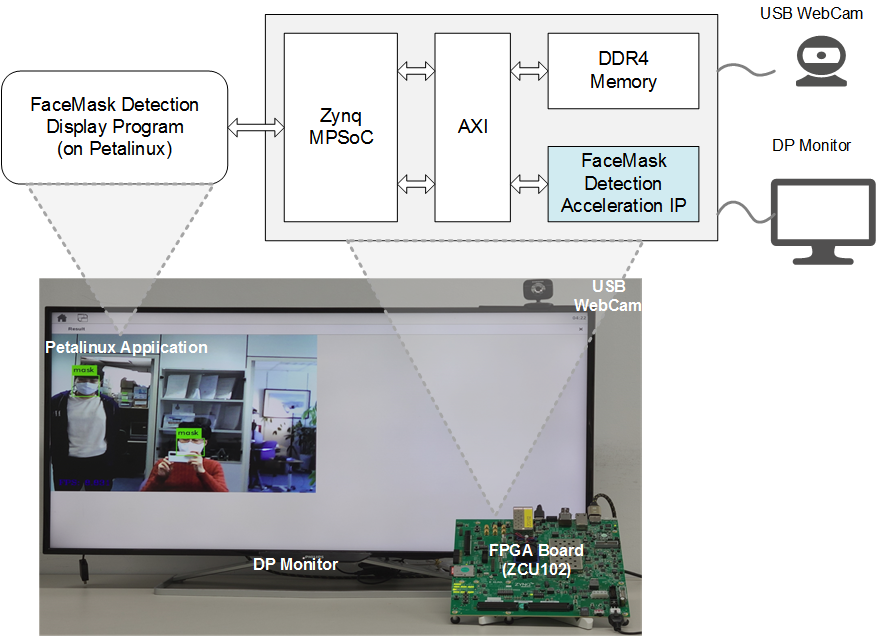

Deep Learning Acceleration for Edge-Computing: Facemask detection on stand-alone FPGA (Feb. 2021)

-

Future Design Systems announced facemask detection application of deep learning acceration for edge-computing using ZCU102, in which deep learning object detection inference engine is running in the FPGA.

-

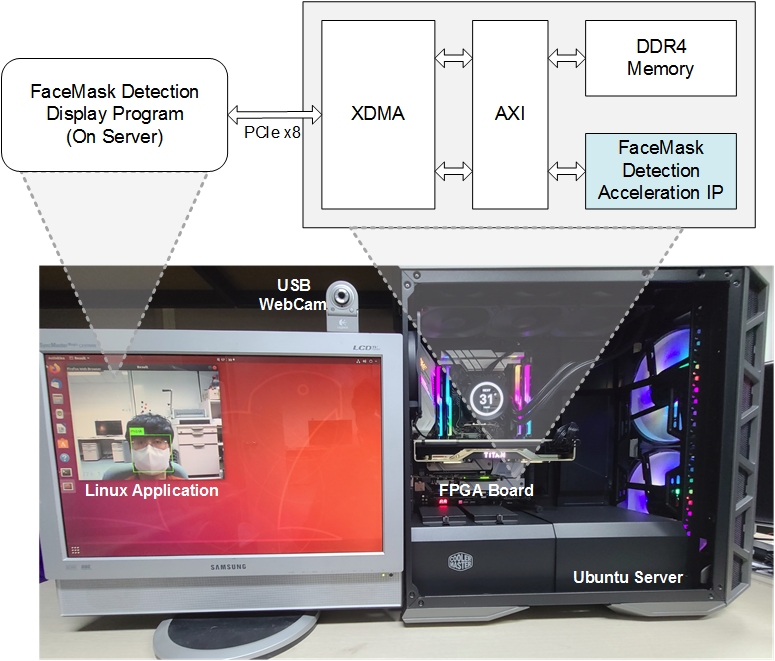

Deep Learning Acceleration for Server: Facemask detection on FPGA through PCI-Express (Jan. 2021)

-

Future Design Systems announced facemask detection application of deep learning acceration for server using DeepAccel, in which deep learning object detection inference engine is running in the FPGA through PCI-Express.

Year 2020 |

AI Development Package (Dec. 2020)

-

New product for Artificial intelligence (AI) / Deep Learning (DL) development package

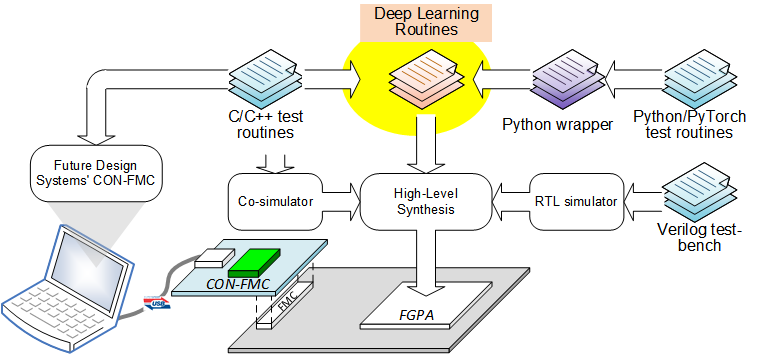

DLR: Deep Learning Routines (Dec. 2020)

-

Future Design Systems announced DLR (Deep Learning Routines) package, which is a collection of high-level synthesizable C routines for deep learning inference network.

Facemask detection inference engine on FPGA (Nov. 2020)

-

Future Design Systems announced an example of running facemask detection on FPGA/DeepAccel-KU/DeepAccel-DualVU9P.

Multi-giga sampling FPGA board (Sept. 2020)

-

Future Design Systems announced an new product for multi-giga sampline of ADC/DAC.

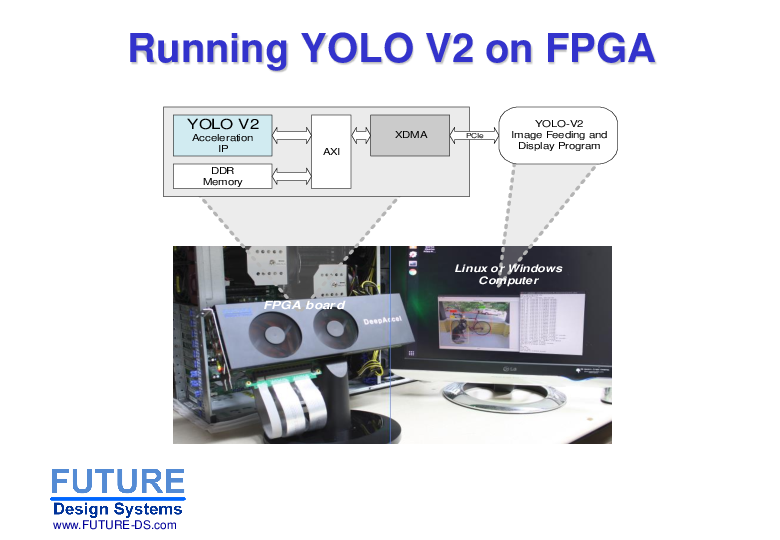

Running YOLO V2 on FPGA through PCI-Express (Jan. 2020)

-

Future Design Systems announced an example of running YOLO V2 on FPGA/DeepAccel-DualVU9P, in which PC (Linux) controls the FPGA through PCI-Express.

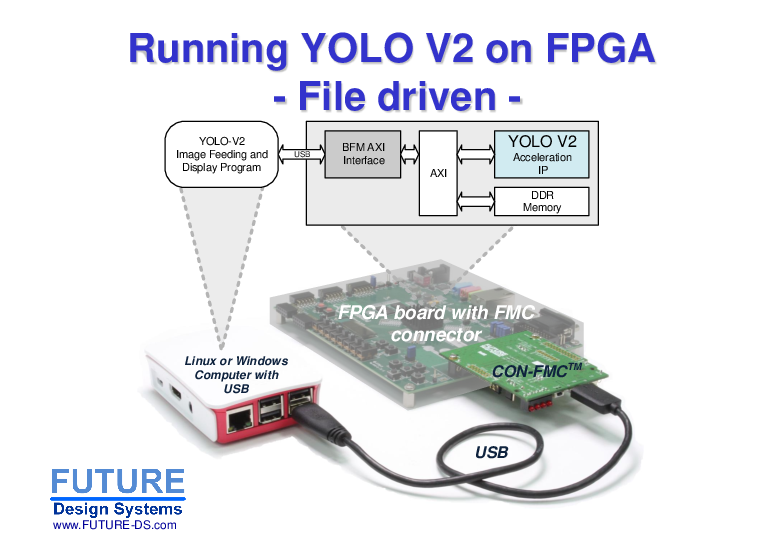

Running YOLO V2 on FPGA using CON-FMCTM (Jan. 2020)

-

Future Design Systems announced a novel approach of YOLO V2 on FPGA, in which Raspberry Pi controls the FPGA through USB/CON-FMC.

-

New Deep-Learning Product Line added (Jan. 2020)

-

Future Design Systems adds new product line for Deep-Learning accelerator; DeepAccel-DualVU9P.

-

Year 2020

-

Year 2020 of Future Design Systems will be a turning point.

Year 2019 |

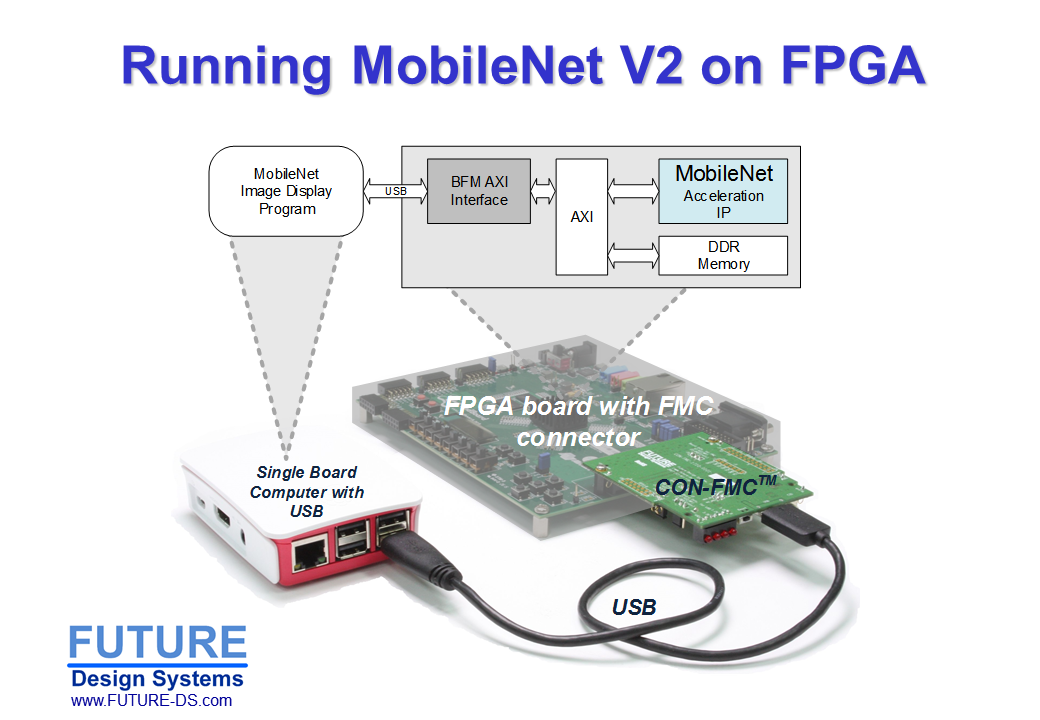

Running MobileNet V2 on FPGA using CON-FMCTM (Dec. 2019)

-

Future Design Systems announced a novel approach to run Deep-Learning application on FPGA, in which Raspberry Pi controls the FPGA through USB/CON-FMC.

Government funnded project on Deep Learning (Dec. 2019)

-

Future Design Systems successfully completed "Development of HPC System for Accelerating Large-Scale Deep Learning" project, which is funded by the Ministry of Science and ICT(MSIT, Korea).

Member of Company University Cooperation Program (2019.12-2020.2)

-

Future Design Systems is taking in part of CUOP program, in which an intern is joined with Future Design Systems.

Successfully completed development of AI accelerator under the contract with SK Telecom (Dec. 2019)

-

Future Design Systems successfully completed dual-FPGA (Xilinx UltraScale+) AI/ML accelerator under the contract with SK Telecom.

Contract with KARI to develop AI accelerator for Cubesat (Nov. 2019)

Future Design Systems contracts with KARI to develop FPGA-based AI accelerator for Cubesat.

Approved as a company running an internship program (2019.9-2019.12)

-

Future Design Systems is taking in part of Internship program with KOSAF.

Member of Industry-Academic Cooperation Foundation Handong Global University (2019.08)

-

We are now a member of Handong Global University IACF. Handong Global University IACF (Industry-Academic Cooperation Foundation).

Member of ICT Internship Program (2019.7-2019.12)

-

Future Design Systems is taking in part of ICT Internship program.

CON-FMC GitHub Repository (June, 2019)

-

Future Design Systems prepares GitHub repository for CON-FMC SW ( Linux and Windows) and examples.

-

Workshop on HSR/PRP and PTP (June 7, 2019)

-

Future Design Systems runs sessions at the workshop hosted by The Korean Institute of Communications and Information Science. The workshop is held at Soongsil University on June 7, 2019. Program

-

Python package for CON-FMC released (Feb. 2019)

-

Python interface package for CON-FMC is ready. This package enables user to run CON-FMC API and functions from Python.

-

Contract with Sejong University to develop D-OCT system (Jan. 2019)

-

Future Design Systems contracts with Sejong University to develop D-OCT system.

-

Year 2019

-

Year 2019 of Future Design Systems will be a remarkable.

Year 2018 |

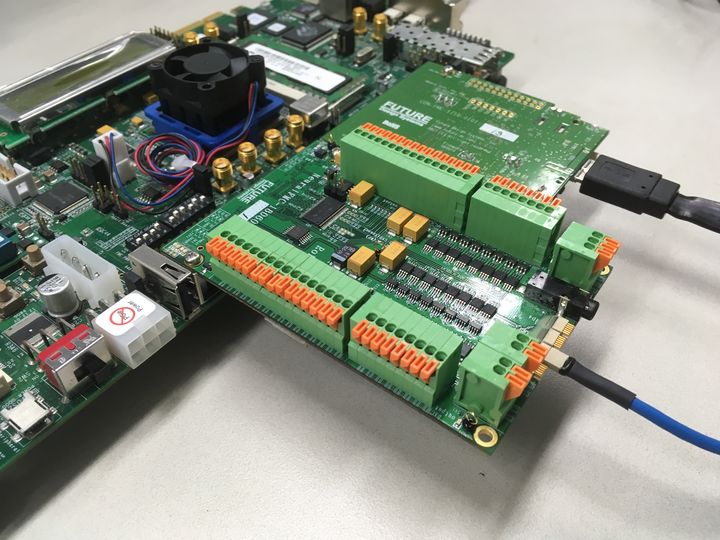

Future Design Systems developed Neural Signal Interface System (Dec. 2018)

-

Future Design Systems developed neural signal interface system. This system consisting of NeuralFMC, FPGA board, and CON-FMC gets neural signals through FPGA and USB3.0. Each NeuralFMC board support up to 128 ADC channels.

-

Patent granted (Dec. 2018)

-

A patent of "APPARATUS AND METHOD FOR COMPUTING A SPARSE MATRIX" is granted. The patent is related with deep-learning computation.

Member of Company University Cooperation Program (2018.12-2019.2)

-

Future Design Systems is taking in part of CUOP program, in which two interns are joined with Future Design Systems.

HSR using FMC-GbE-RJ45 got certificate from TTA (Oct. 2018)

-

Future Design Systems developed IEC 62439-3 HSR (High-availability Seamless Redundancy), which is one of fault tolerant network standards. The HSR products are tested and got certificates by TTA (Telecommunications Technology Association) on Oct. 30, 2018. Future Design Systems has plan to deploy the products in the application areas requires fault tolerance and real-time.

FMC-GbE-RJ45 is released (Oct. 2018)

-

FMC-GbE-RJ45 is ready as a new product. FMC-GbE-RJ45 is an FMC (FPGA Mezzanine Card) board compliant with the VITA 57.1 standard supporting three Gigabit Ethernet ports.

CON-FMC on MagPi Issue 73 page 95 (Sept. 2018)

-

CON-FMC on MagPi Magazin Issue 73 page 95.

MOU on On-Device AI System with SK Telecom (Aug. 2018)

-

Memorandum of Understanding between Future Design Systems and SK Telecom is made on development of On-Devie AI System.

Lecture on OpenCL for seniro engineers (Aug. 2018)"

-

Four-day lecture on OpenCL (Open Computing Language) at FastCampus on April to September. This lecture focuses on OpenCL for Xilinx FPGA and uses AWS EC2 F1 instance.

CON-FMC supports Samsung ARTIK(Aug. 2018)

-

CON-FMC now supporting Samsung ARTIK board.

Contract with SK Telecom to develop AI accelerator (July 2018)

-

Future Design Systems contracts with SK Telecom to develop FPGA-based AI accelerator.

Patents pending(May 2018)

-

Two patents are pending, which are related on computation acceleration of artificial intelligence (deep learning) applications.

Local government funnded project on Neural Siganl (April 2018)

-

Future Design Systems receives a grant from Daejeon Technopark for "Develpment of USB3.0 platform processing neural signals" project.

Lecture on OpenCL: FPGA assisted hardware acceleration for Machine Learning and Deep Learning

-

Two-day public lecture on OpenCL (Open Computing Language) at IDEC KAIST (idec.kaist.ac.kr) on April 3-4, 2018. It includes introduction of OpenCL and hands-on practice using Intel CPU, Xilinx SDAccel for FPGA. The OpenCL examples include vector addition, matrix multiplicaion, convolution, and so on. Each example covers specific topics of OpenCL such as online/offline compilation, optimization using local memory, vector data types, image data type, sychronization, and more.

Member of Xilinx Alliance Program (March 2018)

-

We have been approved as a member of Xilinx Alliance Program for year 2018. The Xilinx Alliance Program is a worldwide ecosystem of qualified companies collaborating with Xilinx to further the development of All Programmable technologies.

Lecture on Artificial Intllegence, Machine Learning, and Deep Learning

-

Two-day public lecture on Deep Learning at IDEC KAIST on Jan. 10-11, 2018. It includes introduction of AI/ML/DL and hands-on practice using TensorFlow, Darknet/YOLO, Tiny-DNN.

Government funnded project on Deep Learning (Jan. 2018)

-

Future Design Systems takes part in "Development of HPC System for Accelerating Large-Scale Deep Learning" project, which is funded by the Ministry of Science and ICT(MSIT, Korea).

-

Year 2018

-

Year 2018 of Future Design Systems will be a next step to the future.

Year 2017 |

Member of Company University Cooperation Program (2017.12-2018.2)

-

We are now a member of CUOP (Company University Cooeration) Program.

-

We have been certified as a valid Symantec EV Codesigning. (2017.12-2018.12)

-

We are now a certified company of Symantec Inc. from COROSSCERT; Korea Electronic Certification Authority Inc.

Member of Xilinx Alliance Program (2017.10)

-

We are now a member of Xilinx Alliance Program. The Xilinx Alliance Program is a worldwide ecosystem of qualified companies collaborating with Xilinx to further the development of All Programmable technologies.

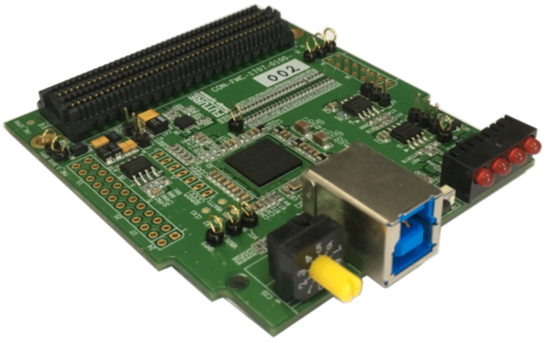

CON-FMC is released (2017.09)

-

CON-FMC is ready as a new product. CON-FMC is a USB 3.0 FMC (FPGA Mezzanine Card) board compliant with the VITA 57.1 standard.

Member of IUCF Hanbat Natioanl University (2017.09)

-

We are now a member of Hanbat Natioanl University IUCF. Hanbat National University IUCF (Industry-University Cooperation Foundation).

Certified as Venture Business (2017.07)

-

We are certified as a Vencture Business from Small and Medium Business Corporation.

Member of OUIC KAIST (2017.06)

-

We are now a member of TBC (Technology Business Incubation Center) of OUIC KAIST. KAIST OUIC (Office of University-Industry Cooperation).

한글

한글