- DPU: Deep Learning Processor Solutions

- OpenCL Solutions

- Machine Learning & Deep Learning Solutions

- Multi-Giga Sampling ADC/DAC Solutions

- Embedded Processor Solutions

- Industrial Network Solutions

- PCI-Express Solutions

- Ethernet Solutions

- USB Solutions

- FPGA-based facemask detection project

- FPGA-based deep-learning accelerator project

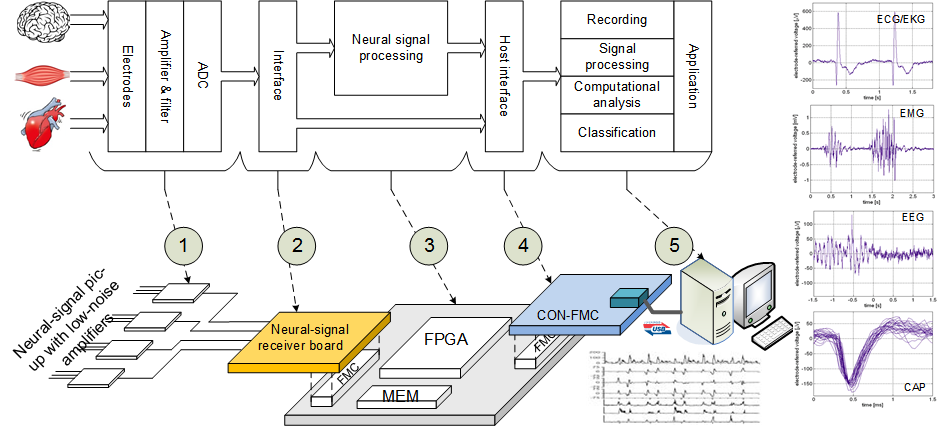

- Neural signal interface platform project

- HSR switch project

DPU Solutions

-

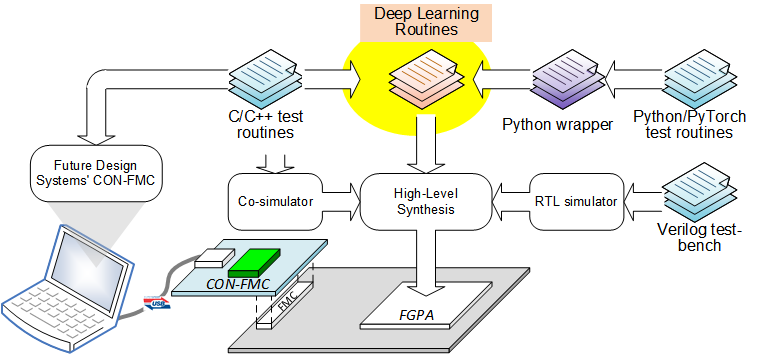

DLR (Deep Learning Routines) as a part of DPU (Deep Learning Processing Unit) is a collection of high-level synthesizable C routines for deep learning inference network. More details to be added.

OpenCL Solutions

-

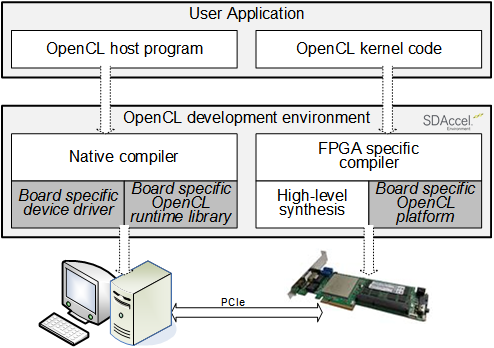

OpenCL supporting platforms.

More details to be added.

Machine Learning & Deep Learning Solutions

-

FPGA-based accelerator.

More details to be added.

Multi-Giga Sampling ADC/DAC Solutions

-

Multi-giga sampling signal processing.

More details to be added.

Embedded Processor Solutions

-

RISC-V and Core-A

More details to be added.

Industrial Network Solutions

-

-

HSR and PTP supporting FPGA board.

More details to be added.

PCI-Express Solutions

-

-

PCI-Express supporting FPGA board, including Gen3 8lanes.

More details to be added.

Ethernet Solutions

-

-

Gigabit Ehternet supporting FPGA board, including copper and optic.

More details to be added.

USB Solutions

-

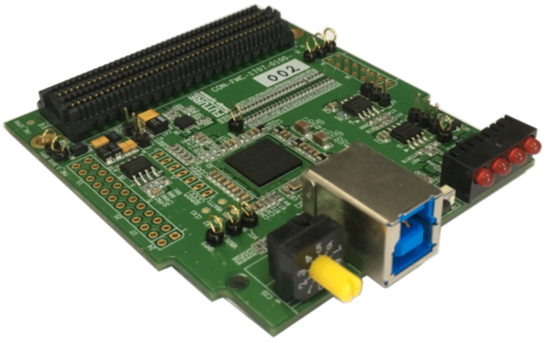

USB 3.0/2.0 supporting FPGA board.

More details to be added.

Facemask detection using deep learning on FPGA

-

-

Facemask detection using deep learning inference that is run on FPGA.

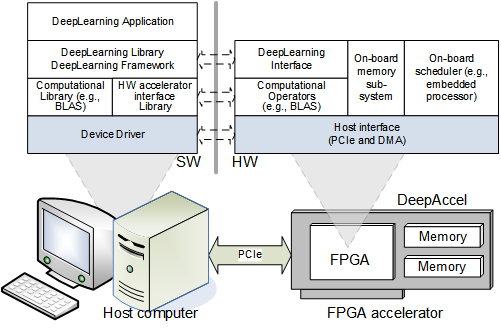

FPGA-based deep-learning accelerator

-

-

FPGA-based accelerator for the project "HPC System for High-speed & Large-scale Deep Learning (2016~2019)", which is funded by the the Ministry of Science and ICT (MSIT, Korea).

Development of HPC (High Performance Computing) system with high-speed and distributed training framework for large-scale deep learning based on computation and communication accelerator specialized for deep learning. This project is led by ETRI (High Performance Computing Research Department, Infra/Core Software Technology Research Division, SW-Contents Research Laboratory) and carried out by Future Design Systems, DevStack, Hilaris, PDXen, Cosmnet, KAIST, and SNU (Seoul National University). Future Design Systems takes part in development of FPGA-based acceleator, which is PCI-Express FPGA board supporting deep learning frameworks such as TensoFlow, Caffe, and so on.

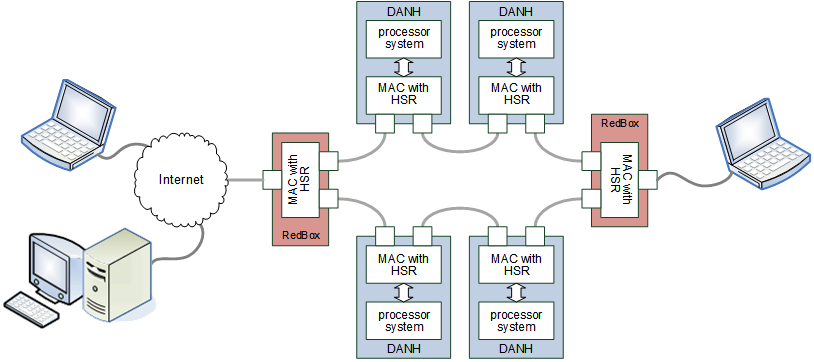

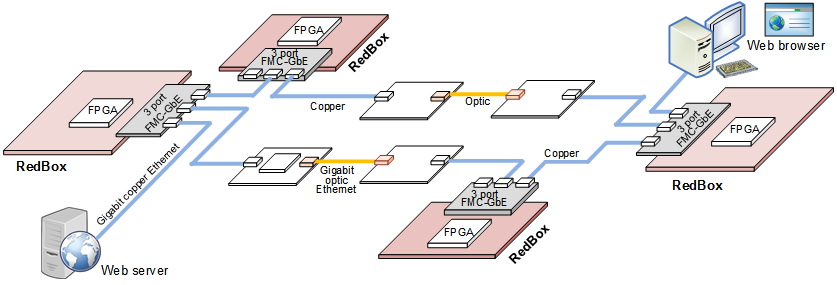

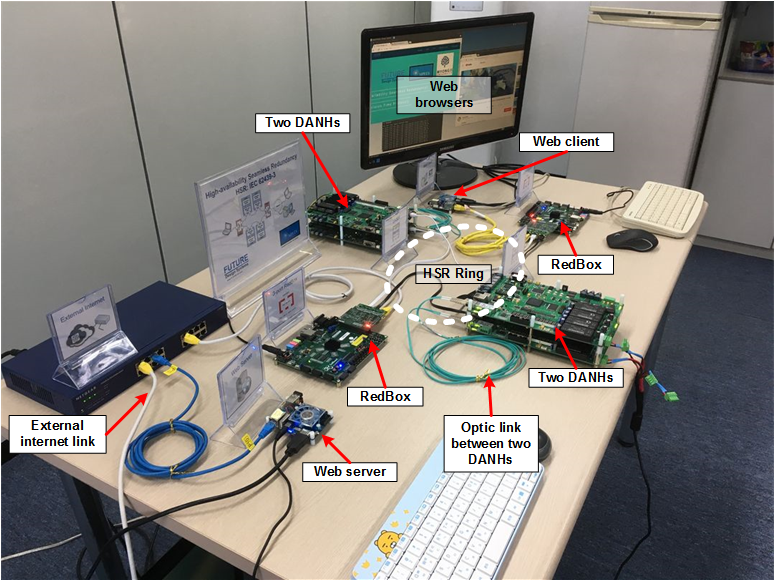

HSR Switch

-

-

HSR switch project "HSR Switch for Smart Grid that Significantly Improves Traffic Performance (2016~2017)", which is partially funded by the Ministry of Science and ICT (MSIT, Korea).

This project is led by MPEES and carried out by Future Design Systems and MyongJi University. This project focuses on development of HSR (High-available Seamless Redundancy, IEC-62439-3) based on Gigabit Ethernet and applies QR (Quick Removing) feature in order to reduce traffic overhead. Future Design Systems takes part in developing HSR platform using FPGA.High-availability Seamless Redundancy (HSR) is a network protocol for Ethernet that provides seamless failover against failure of any network component.

HSR은 네트웍 소자의 고장을 바로 복구하는 이더넷용 네트웍 프로토콜이다.

-

-

An implementation of IEC 62439-3 (HSR) with QR (Quick Remove) feature using FMC-GbE-RJ45, which reduces up to 50% network traffic.

QR 기능을 추가한 IEC62439-3 (HSR) 표준을 구현하여 네트웍 통신량을 최대 50%까지 줄인다.

This picture and photo show a schematic view and a real setup of the demonstation, consisting of two RedBoxes and four DANHs.

The computer (as web client) access the other computer (as web server) using ping and web browser through HSR ring even though one of HSR link is disconnected.

한글

한글